## M21528-13

## Dual 3G/HD/SD-SDI Multi-rate Video Cable Driver

#### Rev V4

#### **Applications**

- 3G/HD/SD Video Switchers

- · 3G/HD/SD Video Routers

- 3G/HD/SD Distribution Amplifiers

- DVB-ASI Equipment

- SMPTE 259C/D, 292M, 424M, DVB ASI 270Mb/s

#### **Features**

- Dual channel cable driver

- Two pairs of non-inverting, SMPTE compliant outputs

- Typical output jitter of 12 ps peak-to-peak at 2.97 Gbps

- · Exceptional Output Return Loss with no matching network

- · Very low power design; 40 mW/channel @1.8V

- · Selectable slew rate for SD and 3G/HD operation

- · Input equalization for up to 36" of FR4 + 2 connectors

- Integrated, selectable  $75\Omega$  or  $50\Omega$  output termination

- Integrated  $50\Omega$  input termination

- Integrated 2x2 crosspoint switch with broadcast mode

- On-chip regulators for operation from 1.8V to 3.3V DC supply

- Universal DC coupling at the input, from 1.2V to 3.3V

- Cable detect with automatic power down and power up upon cable disconnect and re-connect

- · Loss of input signal detection

- · Independent channel mute and power down

- Industrial operating temperature range: -40°C to 85°C

- 4 kV HBM and 500V CDM ESD rating

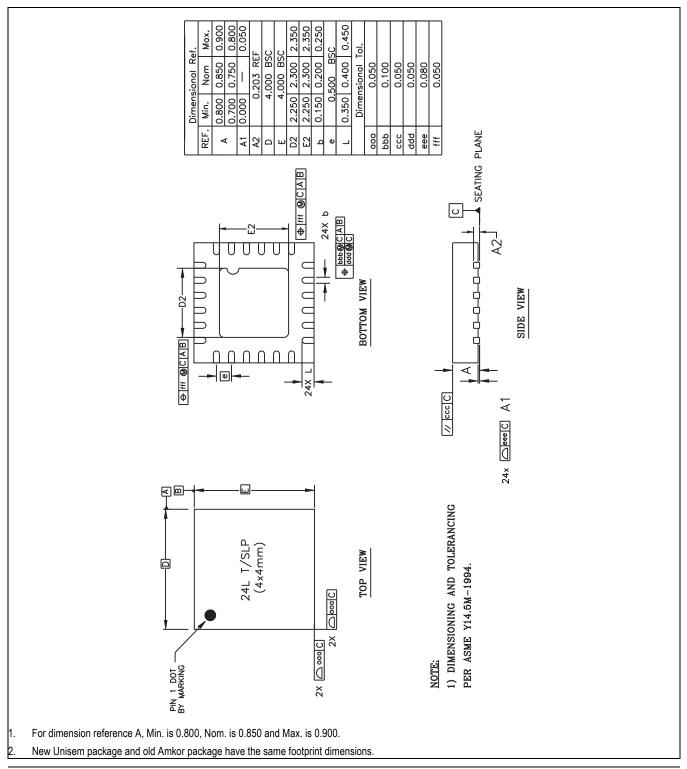

- 4 mm x 4 mm 24 pin QFN package

- Green and RoHS compliant

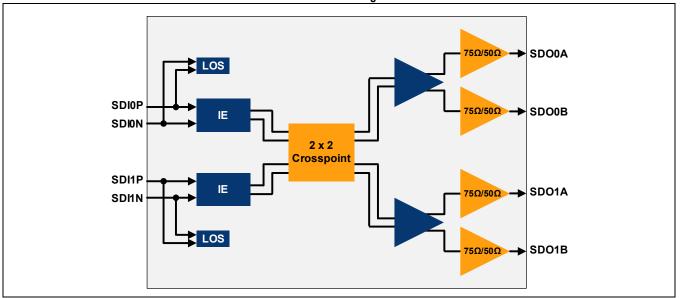

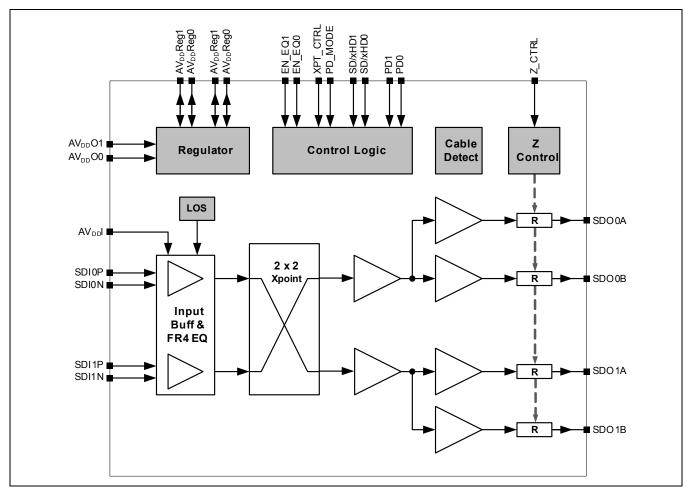

The M21528 is a very low power, highly integrated, dual cable driver for SMPTE compliant digital video applications. It can drive 2 pairs of 75 $\Omega$  coaxial cables, or 50 $\Omega$  equivalent loads, at SDI data rates from 270 Mbps to 2.97 Gbps. The device is capable of outputting SDI signals with typical jitter values of 12 ps peak-to-peak, when operating at 2.97 Gbps.

The dual cable driver includes a 2x2 input crosspoint and integrated input and output termination resistors. The M21528, with input equalization for up to 36" of FR4 trace in addition to two connectors and exceptional Output Return Loss (ORL), is ideal for high speed, 3G-SDI, designs.

The device features integrated supply regulators, allowing it to be powered from 1.8V, 2.5V, or 3.3V supply voltages. When operating at 1.8V, it consumes only 40 mW per channel at 2.97 Gbps. Furthermore, the power rails for the input and output circuitry are electrically isolated on-chip and as such may be connected to different voltage rails on the board. This feature enables the M21528 to be DC coupled to any upstream device in the 1.2V to 3.3V range.

The integrated 2x2 crosspoint allows for either input to be routed to either output, eliminating the need for an external multiplexer. Additionally, one input may be routed to both outputs. The cable driver also provides cable detect and Loss of Signal (LOS) functionality. It can be configured to automatically power down at cable disconnect or loss of input signal.

The M21528 is offered in a green and RoHS compliant 24 pin QFN package.

M21528 Block Diagram

1

## **Ordering Information**

| Part Number                                                                                                                                                                     | Package                                 | Operating Temperature |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------|--|--|--|

| M21528G-13                                                                                                                                                                      | 4 mm x 4 mm 24-pin QFN (RoHS compliant) | –40 °C to 85 °C       |  |  |  |

| * The letter "G" designator after the part number indicates that the device is RoHS compliant. The RoHS compliant devices are backwards compatible with 225 °C reflow profiles. |                                         |                       |  |  |  |

## **Revision History**

| Revision | Level       | Date          | Description                                                                                                                                                                                                                                         |

|----------|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V4       | Release     | December 2015 | Added footnotes to Figure 3-7.                                                                                                                                                                                                                      |

| V3       | Release     | May 2015      | Revised Z_CTRL resistor value for 75Ω output impedance in Table 3-1.<br>Revised Section 4.3.<br>Updated Marking Diagram.<br>Updated Figure 3-7 with new package diagram.                                                                            |

| E (V2)   | Release     | March 2010    | Corrected Figure 3-7 center pad dimensions.<br>Revised Table 1-5; DRIN min, JAO 3G, HD max.                                                                                                                                                         |

| D (V1)   | Release     | December 2009 | Added marking diagram.<br>Added Eye Diagams in Section 2.0.<br>Revised typical and Maximum values in Table 1-3.<br>Revised Table 1-4.<br>Revised Figure 3-2 and Figure 3-3.                                                                         |

| C (V1P)  | Preliminary | May 2009      | Added Note 5 to Table 1-5.<br>Removed Note 2 from Table 3-1 (2-state/I-Digital inputs have an internal 100K $\Omega$ resistor to AV <sub>DD</sub> I).<br>Revised Figure 4-3, Figure 4-4, Figure 4-5.<br>Added input/output circuits in Section 3.0. |

| B (V2A)  | Advance     | February 2009 | Major revisions throughout document.                                                                                                                                                                                                                |

| A (V1A)  | Advance     | June 2008     | Initial Release.                                                                                                                                                                                                                                    |

#### M21528 Marking Diagram

2

## **Table of Contents**

| Orde  | ring lı | nformation                                        | 2    |

|-------|---------|---------------------------------------------------|------|

| Revis | sion ⊦  | listory                                           | 2    |

| Table | e of C  | ontents                                           | 3    |

| 1.0   | Elec    | trical Characteristics                            | 4    |

| 2.0   | Турі    | cal Performance Characteristics                   | 7    |

| 3.0   | Pino    | out Diagram, Pin Description, and Package Drawing | 8    |

| 4.0   | Fund    | ctional Description                               | . 14 |

|       | 4.1     | Block Diagram                                     |      |

|       | 4.2     | Input Description                                 | 15   |

|       | 4.3     | Output Description                                | 16   |

|       | 4.4     | Power Supply Description                          | 18   |

|       | 4.5     | Logic Control Signals                             | 20   |

|       |         | 4.5.1 Slew Rate Control                           | 20   |

|       |         | 4.5.2 Crosspoint Control                          | 20   |

|       |         | 4.5.3 Powerdown Mode Control                      | 21   |

|       | 4.6     | Cable Detection                                   | 21   |

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

## **1.0 Electrical Characteristics**

Unless noted otherwise, specifications apply for typical recommended operating conditions shown in Table 1-2, with  $AV_{DD}O = 1.8V$ ,  $AV_{DD}I = 1.2V$ , CML inputs at 800 mV differential (RL = 50 $\Omega$ ), PRBS  $2^{15}$  – 1 test pattern at 2.97 Gbps.

| Symbol                | Parameter                                                                                | Note | Minimum | Typical | Maximum                | Unit |  |

|-----------------------|------------------------------------------------------------------------------------------|------|---------|---------|------------------------|------|--|

| AV <sub>DD</sub> I    | Analog supply for input circuitry                                                        |      | -0.5    | _       | 3.6                    | V    |  |

| AV <sub>DD</sub> O0/1 | Analog supply for output circuitry                                                       | 1    | -0.5    | _       | 3.6                    | V    |  |

| T <sub>ST</sub>       | Storage Temperature                                                                      | 1    | -65     | _       | 150                    | °C   |  |

| ESD                   | Human Body Model (HBM)                                                                   | 1    | -4      | _       | 4                      | KV   |  |

| ESD                   | Charge Device Model (CDM)                                                                | 1    | -500    | _       | 500                    | V    |  |

| LU                    | Latch Up @ 85°C                                                                          | 1    | -200    | _       | 200                    | mA   |  |

| HSIC                  | Maximum High-speed input current                                                         | 1    | -100    | _       | 100                    | mA   |  |

| HSOC                  | Maximum High-speed output short circuit current                                          | 1    | -100    | _       | 100                    | mA   |  |

| V <sub>INMAX</sub>    | Input voltage range                                                                      | 1    | -0.5    | _       | AV <sub>DD</sub> I+0.5 | V    |  |

| NOTES:                | IOTES:                                                                                   |      |         |         |                        |      |  |

| 1. Exposure           | Exposure to these conditions over extended periods of time may affect device reliability |      |         |         |                        |      |  |

Table 1-1. Absolute Maximum Ratings

#### Table 1-2. Recommended Operating Conditions

| Symbol                 | Parameter                          | Note | Minimum | Typical                  | Maximum | Unit |  |

|------------------------|------------------------------------|------|---------|--------------------------|---------|------|--|

| AV <sub>DD</sub> I     | Analog supply for input circuitry  | -    | 1.14    | 1.2, 1.8,<br>2.5, or 3.3 | 3.465   | V    |  |

| AV <sub>DD</sub> O0/1  | Analog supply for output circuitry | -    | 1.71    | 1.8, 2.5, or<br>3.3      | 3.465   | V    |  |

| T <sub>CASE</sub>      | Operating temperature              | 1    | -40     | 25                       | +85     | °C   |  |

| ESD                    | Human Body Model (HBM)             | —    | -4      | _                        | 4       | kV   |  |

| NOTES:<br>1. Case term | Casa temporatura                   |      |         |                          |         |      |  |

<sup>4</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

| Symbol                | Parameter                                                             | Conditions                                                                                   | Note | Minimum | Typical | Maximum | Unit |

|-----------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|---------|---------|---------|------|

| P <sub>DISS</sub>     | Total power consumption                                               | $AV_{DD}I = 1.2V$<br>$AV_{DD}O = 1.8V$<br>Both channels active, 4 outputs on                 | 1    | _       | 78      | 122     | mW   |

|                       |                                                                       | $AV_{DD}I = 1.2V$<br>$AV_{DD}O = 1.8V$<br>Both channels active, one output per channel<br>on | 1    | _       | 61      | 95      | mW   |

|                       |                                                                       | $AV_{DD}I = 1.2V$<br>$AV_{DD}O = 1.8V$<br>One channel active, one output on                  | 1    | _       | 49      | 86      | mW   |

| I_ AV <sub>DD</sub> I | Total AV <sub>DD</sub> I supply current                               | AV <sub>DD</sub> I = 1.2V                                                                    | 1    | —       | 1       | 3.0     | mA   |

| I_ AV <sub>DD</sub> I | Total AV <sub>DD</sub> I supply current                               | AV <sub>DD</sub> I = 1.8V                                                                    | 1    | —       | 3       | 7.0     | mA   |

| I_ AV <sub>DD</sub> I | Total AV <sub>DD</sub> I supply current                               | AV <sub>DD</sub> I = 3.3V                                                                    | 1    | —       | 10      | 17.0    | mA   |

| I_ AV <sub>DD</sub> O | Total AV <sub>DD</sub> O supply current                               | Both channels active                                                                         | 1,2  | —       | 43      | 68.0    | mA   |

| I_ AV <sub>DD</sub> O | Total AV <sub>DD</sub> O supply current                               | Only channel 0 active                                                                        | 1,2  | —       | 43      | 68.0    | mA   |

| I_AV <sub>DD</sub> O0 | Total AV <sub>DD</sub> O0 supply current                              | Only channel 1 active                                                                        | 1,2  | —       | 27      | 49.0    | mA   |

| $\theta_{JA}$         | Junction to ambient Thermal Resistance                                |                                                                                              | 3    | —       | 63      | _       | °C/W |

|                       | nended operating condition—see Ta<br>consumption does not change with |                                                                                              |      |         |         |         |      |

| 3. Airflow :          |                                                                       |                                                                                              |      |         |         |         |      |

#### Table 1-3. Power Consumption Specifications

#### Table 1-4. Digital Input Specifications

| Symbol          | Parameter                  |   | Minimum                   | Typical | Maximum                   | Unit |

|-----------------|----------------------------|---|---------------------------|---------|---------------------------|------|

| V <sub>IH</sub> | Input Logic High           | _ | 0.85 x AV <sub>DD</sub> I | _       | AV <sub>DD</sub> I + 0.5  | V    |

| V <sub>IF</sub> | Input Logic Floating State | — | 0.25 x AV <sub>DD</sub> I | _       | 0.75 x AV <sub>DD</sub> I | V    |

| V <sub>IL</sub> | Input Logic Low            | _ | 0                         | _       | 0.15 x AV <sub>DD</sub> I | V    |

| I <sub>IH</sub> | Input Current—Logic High   | _ | -100                      | _       | 100                       | μA   |

| ۱ <sub>IL</sub> | Input Current—Logic Low    | _ | -100                      | -       | 100                       | μΑ   |

Rev V4

| Symbol                         | Parameter                               | Note  | Minimum                  | Typical | Maximum                  | Unit |

|--------------------------------|-----------------------------------------|-------|--------------------------|---------|--------------------------|------|

| V <sub>O</sub>                 | Output Voltage Range                    | 1     | 730                      | 800     | 850                      | mV   |

| t <sub>r</sub> /t <sub>f</sub> | SD Rise/Fall Time (20–80%)              | 1,3,4 | 400                      | 600     | 800                      | ps   |

| t <sub>r</sub> /t <sub>f</sub> | 3G/HD Rise/Fall Time (20-80%)           | 1     | _                        | 70      | 90                       | ps   |

| t <sub>r</sub> -t <sub>f</sub> | SD Rise/Fall Time Mismatch              | 1,3,4 | _                        | _       | 125                      | ps   |

| t <sub>r</sub> -t <sub>f</sub> | 3G/HD Rise/Fall Time Mismatch           | 1,3   | _                        | -       | 30                       | ps   |

| DCD                            | Duty Cycle Distortion, SD               | 1,4   | _                        | -       | 100                      | ps   |

| DCD                            | Duty Cycle Distortion, 3G, HD           | 1,3   | _                        | -       | 30                       | ps   |

| JAO <sub>PP</sub>              | Additive Output Jitter, SD              | 1,2,4 | _                        | 60      | 100                      | ps   |

| JAO <sub>PP</sub>              | Additive Output Jitter, 3G, HD          | 1,2   | _                        | 12      | 29                       | ps   |

| S <sub>22</sub>                | Output Return Loss (5 MHz to 1.5 GHz)   | 6,8   | 20                       | -       | -                        | dB   |

| S <sub>22</sub>                | Output Return Loss (5 MHz to 3.0 GHz)   | 5,8   | 11                       | -       | -                        | dB   |

| S <sub>22</sub>                | Output Return Loss (5 MHz to 3.0 GHz)   | 6,8   | 14                       | -       | -                        | dB   |

| DR <sub>IN</sub>               | Input Data rate                         | -     | 270                      | -       | 2970                     | Mbps |

| V <sub>ID</sub>                | Differential Input Voltage (p-p)        | 7     | 400                      | -       | 1600                     | mV   |

| V <sub>IC</sub>                | Input Common mode range                 | -     | AV <sub>DD</sub> I – 0.6 | -       | AV <sub>DD</sub> I + 0.1 | V    |

| IE                             | Input Equalizer Gain Off (EN_EQ = 0)    |       | _                        | 0       | _                        | dB   |

|                                | Input Equalizer Gain Med (EN_EQ = F)    | -     | _                        | 4       | _                        | dB   |

|                                | Input Equalizer Gain High (EN_EQ = H)   |       | _                        | 6       | _                        | dB   |

| R <sub>INT</sub>               | Input Termination to AV <sub>DD</sub> I | _     | 40                       | 50      | 60                       | Ω    |

#### Table 1-5. High Speed Input/Output Electrical Specifications

NOTES:

1. Measured AC coupled into 1m coaxial cable, terminated with appropriate  $75\Omega$  or  $50\Omega$  load.

2. Measured with PRBS 2<sup>15</sup>-1 test pattern.

3. For data rates above 360 Mb/s, the cable driver must be in HD mode (SD/xHD = 0).

4. SD/xHD = 1, measured at 270 Mb/s.

5. Without external matching network.

$\mbox{6.} \qquad \mbox{With external matching network $R_{matching}$=$75$\Omega$, $L_{matching}$=$1nH$, only applicable to $75$\Omega$ mode. } \label{eq:linear}$

7. EQ\_EN = L (input equalization off) PD\_MODE = F (LOS enabled), point blank.

8. As measured on MACOM EVM at BNC connector with output impedance set to  $75\Omega$ .

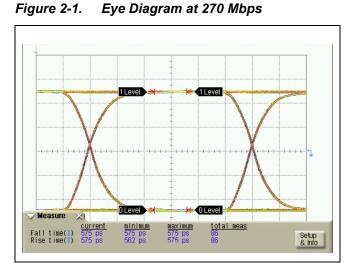

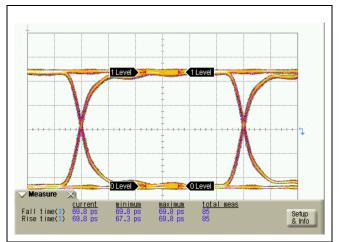

## 2.0 Typical Performance Characteristics

Figure 2-3. Eye Diagram at 2970 Mbps

Figure 2-2. Eye Diagram at 1485 Mbps

<sup>7</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

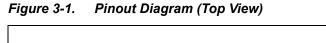

# 3.0 Pinout Diagram, Pin Description, and Package Drawing

Rev V4

| Table 3-1. | Pin Description (1 of 2) |

|------------|--------------------------|

|------------|--------------------------|

| Pin Name              | Pin Number           | Туре              | Description                                                                                                                                                                                               |

|-----------------------|----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AV <sub>SS</sub>      | Center Ground Paddle | Power             | Chip Ground                                                                                                                                                                                               |

| AV <sub>DD</sub> I    | 9                    | Power             | Positive supply for inputs circuitry                                                                                                                                                                      |

| AV <sub>DD</sub> Reg0 | 17,20                | Power             | Regulator0 bypass capacitor connection, positive supply for output0                                                                                                                                       |

| AV <sub>DD</sub> Reg1 | 11,14                | Power             | Regulator1 bypass capacitor connection, positive supply for output1                                                                                                                                       |

| AV <sub>DD</sub> O0   | 16                   | Power             | Positive supply for reglator0                                                                                                                                                                             |

| AV <sub>DD</sub> O1   | 15                   | Power             | Positive supply for reglator1                                                                                                                                                                             |

|                       |                      |                   |                                                                                                                                                                                                           |

| SD00A                 | 19                   | O-Analog          | High speed serial output, channel0, output A                                                                                                                                                              |

| SD00B                 | 18                   | O-Analog          | High speed serial output, channel0, output B                                                                                                                                                              |

| SDO1A                 | 12                   | O-Analog          | High speed serial output, channel1, output A                                                                                                                                                              |

| SDO1B                 | 13                   | O-Analog          | High speed serial output, channel1 output B                                                                                                                                                               |

| SDI0P/N               | 1,2                  | I-Analog          | High speed serial video data input, channel0                                                                                                                                                              |

| SDI1P/N               | 5,6                  | I-Analog          | High speed serial video data input, channel1                                                                                                                                                              |

| Z_CTRL                | 22                   | I-Analog          | Sets output impedance through an external Z_CTRL resistor<br>connected to $AV_{SS}$<br>Z_CTRL=665 $\Omega$ to set 75 $\Omega$ output impedance<br>Z_CTRL=250 $\Omega$ to set 50 $\Omega$ output impedance |

| SD/xHD0               | 24                   | I-DIGITAL         | Output slew rate control for channel 0<br>L = SDO0 has 3G/HD slew rate<br>H = SDO0 has SD slew rate                                                                                                       |

| SD/xHD1               | 7                    | I-DIGITAL         | Output slew rate control for channel 1<br>L = SDO1 has 3G/HD slew rate<br>H = SDO1 has SD slew rate                                                                                                       |

| PD0                   | 23                   | 3-state/I-DIGITAL | Power down control for channel 0<br>L = SDO0A on, SDO0B power down<br>F = Both outputs on<br>H = Power down both outputs                                                                                  |

| PD1                   | 8                    | 3-state/I-DIGITAL | Power down control for channel 1<br>L = SDO1A on, SDO1B power down<br>F = Both outputs on<br>H = Power down both outputs                                                                                  |

| XPT_CTRL              | 21                   | 3-state/I-DIGITAL | Crosspoint control<br>L = SDI0 to SDO1, SDI1 to SDO0<br>F = SDI0 to SDO0, SDI1 to SDO1<br>H = SDI0 to SDO0 and SDO1                                                                                       |

<sup>9</sup>

#### Table 3-1.Pin Description (2 of 2)

| Pin Name                    | Pin Number           | Туре              | Description                                                                                                                                        |

|-----------------------------|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PD_MODE                     | 10                   | 3-state/I-DIGITAL | Power down and cable detect control                                                                                                                |

|                             |                      |                   | L = Cable detect disabled, PD upon LOS disabled<br>F = Cable detect enabled, PD upon LOS enabled<br>H = Cable detect enabled, PD upon LOS disabled |

| EN_EQ0                      | 3                    | 3-state/I-DIGITAL | Input equalization control for channel 0                                                                                                           |

|                             |                      |                   | L = No Input Equalization on SDI0P/N<br>F = Medium Input Equalization on SDI0P/N<br>H = High Input Equalization on SDI0P/N                         |

| EN_EQ1                      | 4                    | 3-state/I-DIGITAL | Input equalization control for channel 1                                                                                                           |

|                             |                      |                   | L = No Input Equalization on SDI1P/N<br>F = Medium Input Equalization on SDI1P/N<br>H = High Input Equalization on SDI1P/N                         |

| OTES:                       | I                    |                   |                                                                                                                                                    |

| 3-state inputs have a defau | ult of F (floating). |                   |                                                                                                                                                    |

|                             |                      |                   |                                                                                                                                                    |

2. A Z\_CTRL resistance of 665Ω will also provide 800mVpp output swing.

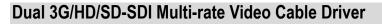

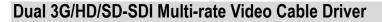

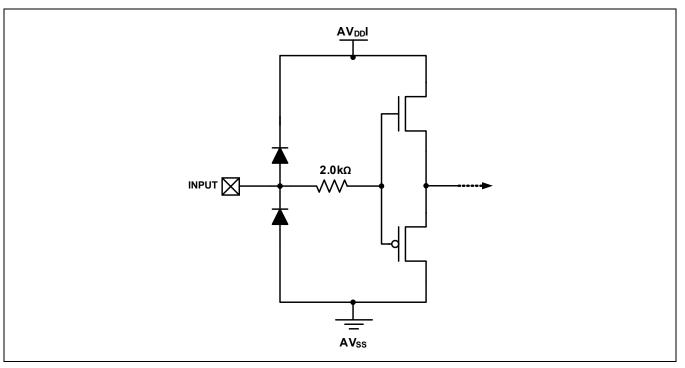

#### Figure 3-2. Differential Input (SDIP, SDIN)

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

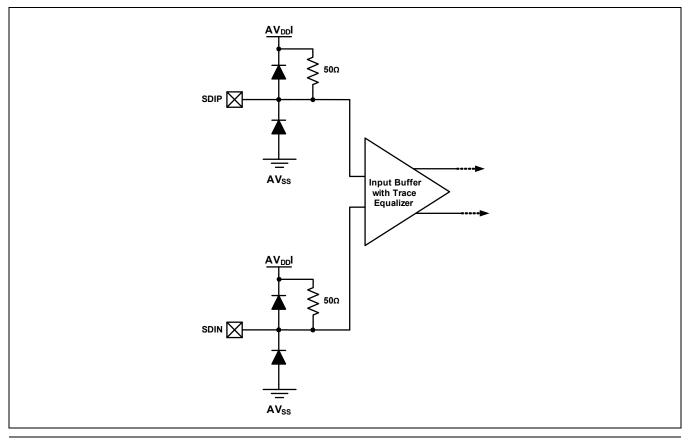

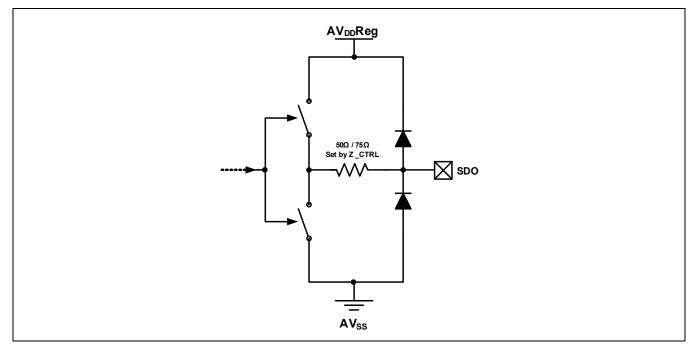

#### Figure 3-3. Single-Ended Output (SDO0A, SDO0B, SDO1A, SDO1B)

Figure 3-4. Digital Input Pin (SD/xHD0, SD/xHD1)

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

## M21528-13

Rev V4

### Dual 3G/HD/SD-SDI Multi-rate Video Cable Driver

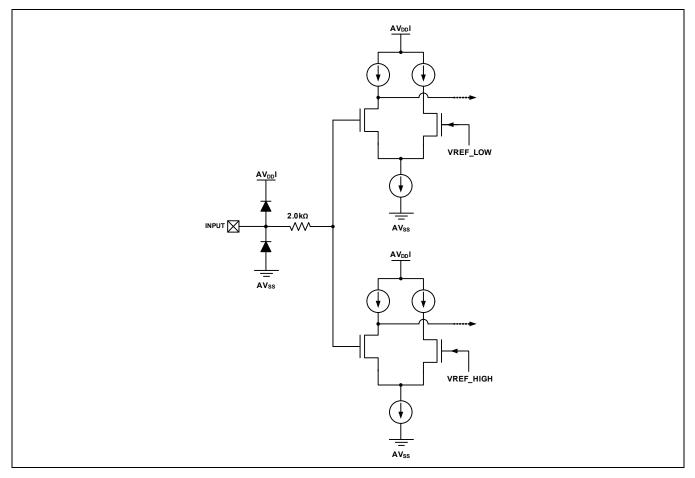

#### Figure 3-5. State Logic Input (PD0, PD1, XPT\_CTRL, PD\_MODE, EN\_EQ0, EN\_EQ1)

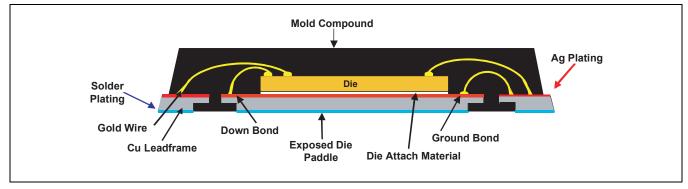

The M21528 is assembled in 24 pin 4 mm x 4 mm Quad Flat No-Lead (QFN) package. The exposed die paddle serves as the IC ground ( $AV_{SS}$ ), and the primary means of thermal dissipation. This die paddle should be soldered to the PCB ground. A cross-section of the QFN package can be found in Figure 3-6.

Figure 3-6. QFN Package Cross Section

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

#### Figure 3-7. Package Drawing

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

13

MACOM

## 4.0 Functional Description

## 4.1 Block Diagram

Figure 4-1 is the functional block diagram of the M21528. The subsequent sections provide additional detail on the operation of the device.

Figure 4-1. M21528 Functional Block Diagram

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

## 4.2 Input Description

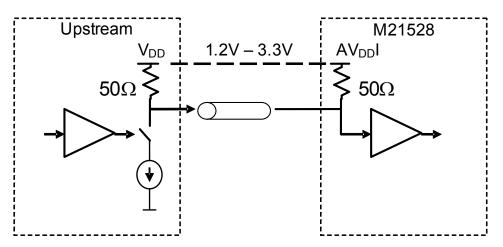

The M21528 has differential inputs, with integrated 50 $\Omega$  pull ups to AV<sub>DD</sub>I. AV<sub>DD</sub>I may be supplied from a 1.2V, 1.8V, 2.5V, or 3.3V supply. The input buffers are compatible with PCML, LVDS or LVPECL signal levels.

To improve signal integrity in large systems, all inputs have programmable input equalization (IE) with three gain levels: 0 dB, 4 dB, 6 dB.

Setting the gain to 0dB effectively disables the IE feature. The pins EN\_EQ0 and EN\_EQ1 allow for the selecting the proper level of input equalization based on the board characteristics for each input. The maximum level of equalization compensates for up to 36" of FR4 trace. The operation of the EN\_EQ0/1 pin is summarized in Table 4-1 below.

| Pin    | Level | Function                  |

|--------|-------|---------------------------|

| EN_EQ0 | L     | SDI0P/N IE EQ gain = 0 dB |

|        | F     | SDI0P/N IE EQ gain = 4 dB |

|        | Н     | SDI0P/N IE EQ gain = 6 dB |

| EN_EQ1 | L     | SDI1P/N IE EQ gain = 0 dB |

|        | F     | SDI1P/N IE EQ gain = 4 dB |

|        | Н     | SDI1P/N IE EQ gain = 6 dB |

Table 4-1.

Operation of EQ\_EN0 and EQ\_EN1 Pins

In 3G/HD/SD SDI applications, it is best to avoid AC coupling data interfaces between devices, if possible. DC coupling will result in increased system jitter margin. Also, DC coupling eliminates the requirement for additional components on the board. In order to accommodate DC coupling to the upstream device, the  $AV_{DD}I$  domain of the M21528 is electrically isolated from all other power domains on chip. This allows for it to be tied to the V<sub>DD</sub> of the previous device's driver enabling a fully DC coupled system, as shown below.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

## M21528-13

### Dual 3G/HD/SD-SDI Multi-rate Video Cable Driver

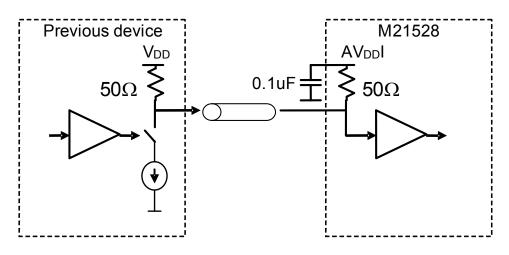

Alternatively, a "self-biasing" scheme can be used at the input. This offers the benefit of having the  $V_{DD}$  of the previous device and the power domain(s) of the M21528 completely separated, while allowing dc coupling:

In this configuration, the minimum input common mode that can be tolerated, is 1.2V.

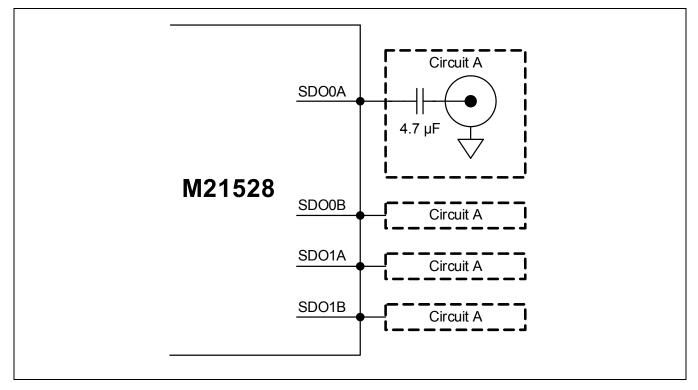

If, for any reason, AC coupling is necessary, then a capacitor of 4.7  $\mu F$  or greater must be used.

A Loss of Signal (LOS) detector circuit monitors each input and issues an internal alarm when the input signal goes below the detection threshold. The detection threshold is 90 mVpp with +90 mV hysteresis. This means that if the input signal level drops below 90 mVpp, then the internal LOS alarm is asserted. For the alarm to be de-asserted, the input signal must increase to greater than 180 mVpp; the hysteresis prevents the internal LOS alarm from chattering.

Depending on the state of the PD\_MODE pin, the LOS alarm at a particular input can power down the associated signal path and forces the corresponding output to low level.

## 4.3 Output Description

The M21528 contains two independent signal channels, each with two positive polarity cable driver outputs. Unlike conventional SMPTE compliant cable drivers, the M21528 uses a voltage mode implementation as opposed to current mode. This allows for significant power savings when compared to previous generation cable drivers with the added benefit of two positive polarity outputs per channel.

Internally an output buffer drives a 1.6V amplitude signal through an integrated impedance load. The impedance of the load is set by the external Z\_CTRL resistor to AV<sub>SS</sub>. For most applications Z\_CTRL should be 665 $\Omega$ , which sets the output load to 75 $\Omega$  and provides 800mVpp output swing. If the application requires a 50 $\Omega$  output impedance, Z\_CTRL may be 250 $\Omega$ . In both cases Z\_CTRL must have 1% tolerance.

The M21528 can meet SMPTE ORL specifications without the need for an external matching network. However, for additional margin a matching network consisting of a  $75\Omega$  resistor and a 1 nH inductor may be used.

Each channel has a dedicated power down pin, PD0 and PD1. The operation of the PD pin is summarized in Table 4-2 below. When powered down, the signal at the output is set to low.

Rev V4

<sup>16</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

| Pin | Level | Function                          |

|-----|-------|-----------------------------------|

| PD0 | L     | SDO0A on, SDO0B powered down      |

|     | F     | Both SDO0A and SDO0B on           |

|     | Н     | Both SDO0A and SDO0B powered down |

| PD1 | L     | SDO1A on, SDO1B powered down      |

|     | F     | Both SDO1A and SDO1B on           |

|     | Н     | Both SDO1A and SDO1B powered down |

#### Table 4-2.Operation of PD0 and PD1 Pins

Figure 4-2 shows a typical output circuit.

When the cable detect function is enabled, only the outputs used need to be connected, unused outputs may be left floating.

However, if the cable detection function is disabled, unused outputs must be powered down or properly terminated.

#### Figure 4-2. Typical Output Circuit (all outputs connected)

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

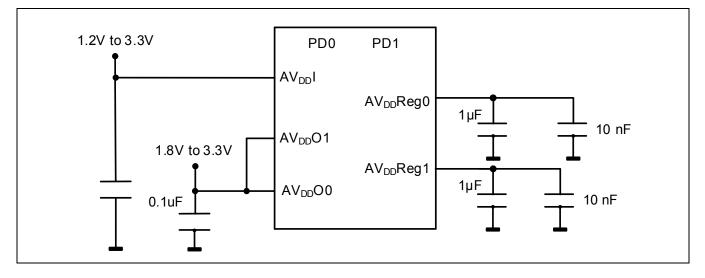

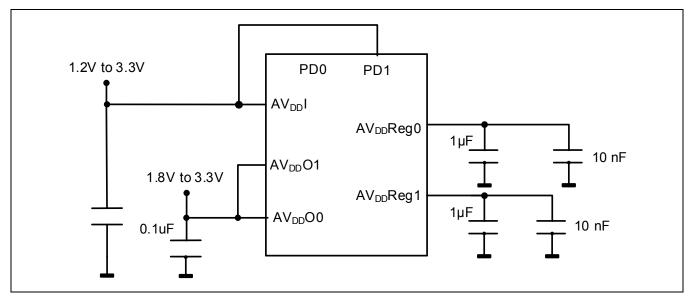

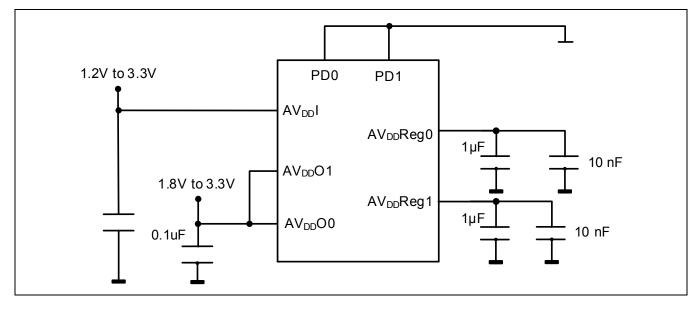

## 4.4 **Power Supply Description**

The device features two internal regulators to supply the power for the output drivers for each channel.  $AV_{DD}O0$  and  $AV_{DD}O1$  supply the voltage to each channel's respective regulator. These pins may be connected to DC voltages ranging from 1.8V to 3.3V. Each regulator requires an external 1µF bypass capacitor to ground, which must be connected to  $AV_{DD}Reg0$  and  $AV_{DD}Reg1$ . It is recommended to add a secondary 10 nF bypass capacitor on each regulator output as close to the pin as possible.

In addition to supplying the output stage for channel1,  $AV_{DD}O1$  is also used to power the core circuitry for both channels.

A completely separate supply domain,  $AV_{DD}I$ , provides the supply for the high-speed serial input pins. The input termination and ESD protection for the SDI pins and the digital control input pins are referenced to this supply. The isolated domain allows DC coupling to an upstream device that is running from a different supply voltage. For example, if, in order to save power,  $AV_{DD}O0/1$  are connected to 1.8V, but the cable driver must interface to a reclocker that uses a 3.3V supply, then DC coupling can be achieved by simply connecting  $AV_{DD}I$  to the 3.3V rail.

Figure 4-3 to 4-5 show three examples of how the cable driver can be configured. Note that even when only one channel is enabled, both output regulators must be supplied with the correct voltage.

Figure 4-3. Supply configuration, both channels and both A and B outputs used

## M21528-13

Rev V4

### Dual 3G/HD/SD-SDI Multi-rate Video Cable Driver

#### Figure 4-4. Supply configuration, channel0, outputs A and B used, channel 1 powered down

#### Figure 4-5. Supply configuration, both channels used, but only A outputs used

## 4.5 Logic Control Signals

The digital logic control signals are ESD protected and referenced to the AV<sub>DD</sub>I. This allows the device to interface to many different logic levels from different supply domains.

Some pins have a state called "F"; this stands for "floating". To assert this state leave the pin unconnected.

## 4.5.1 Slew Rate Control

Pins SD/xHD0 and SD/xHD1 control the slew rate of the associated channel outputs. To comply with the SMPTE SD specification the slew rate is slowed down to approximately 600 ps when in SD mode. Note that there is no pullup on the SD/xHD pins, so it should not be left floating.

Table 4-3. Operation of SD/xHD0 and SD/xHD1 Pins

| Pin     | Level | Function                              |

|---------|-------|---------------------------------------|

| SD/xHD0 | L     | Set SDO0A/B Slew rate to 3G/HD Levels |

|         | Н     | Set SDO0A/B Slew rate to SD Levels    |

| SD/xHD1 | L     | Set SDO1A/B Slew rate to 3G/HD Levels |

|         | Н     | Set SDO1A/B Slew rate to SD Levels    |

## 4.5.2 Crosspoint Control

The XPT\_CTRL pin controls the 2 x 2 crosspoint at the input. It can be used to redirect the input signal to the other output or from channel 0 to make broadcast mode, so the input on channel 0 appears on both channel 0 and 1 outputs. This last mode is useful in distribution amplifiers where one input can drive fours positive outputs.

The crossover feature can be used in routers to select a second input bank. The functionality of the XPT\_CTRL pin is summarized in the table below.

Table 4-4.Operation of XPT\_CTRL Pin

| Pin      | Level | Function                                                      |

|----------|-------|---------------------------------------------------------------|

| XPT_CTRL | L     | Crossover mode:<br>SDI0 routed to SDO1<br>SDI1 routed to SDO0 |

|          | F     | Default mode:<br>SDI0 routed to SDO0<br>SDI1 routed to SDO1   |

|          | Н     | Broadcast mode:<br>SDI0 routed to SDO0 and SDO1               |

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

### 4.5.3 Powerdown Mode Control

The M21528 has integrated output cable detection and input LOS detection circuitry. Depending on the setting of the PD\_MODE pin, the device can automatically power down each channel when output cables are disconnected or there is no signal present at the input.

The functionality of the PD\_MODE pin is summarized in the table below.

Table 4-5.Operation of PD\_MODE

| Pin     | Level | Function                   |

|---------|-------|----------------------------|

| PD_MODE | L     | Cable detection disabled   |

|         |       | Power down on LOS disabled |

|         | F     | Cable detection enabled    |

|         |       | Power down on LOS enabled  |

|         | Н     | Cable detection enabled    |

|         |       | Power down on LOS disabled |

## 4.6 Cable Detection

The M21528 features an integrated near-end cable detector. This circuit can detect whether a cable has been disconnected from an output and whether or not it is reconnected without requiring any additional external components.

Utilizing the cable detection feature has several system level advantages such as:

- Reduced power consumption when no cable is connected to both outputs of a single channel

- Reduced EMI

- Eliminate the requirement for external termination

Depending on the state of the PD\_MODE pin, when both output A and B of either channel are disconnected, the device can automatically power down the channel resulting in a 75% power reduction for that channel. Furthermore, if output B is manually powered down (PD = L), then disconnecting output A will result in completely powering down the channel (both outputs).

Due to the detection mechanism, the signal at each output within a channel will experience a phase step of approximately 15 ps when the other output's state is changed: powered down, powered up, disconnected, or reconnected.

If one output is disconnected but the other remains connected, and both outputs are toggling, the signal at the connected output may experience up to 10% overshoot for a period of approximately 500 ns. The overshoot is caused by the reflections coupled from the unconnected output to the connected one. 500 ns is the duration required by the circuit to detect the disconnection. If cable detection is disabled and the output is not properly terminated, the overshoot will persist. Therefore, it is strongly recommended to enable cable detection, or terminate both outputs properly; when both outputs of one channel are turned on.

The cable detection function may be disabled by setting PD\_MODE=L.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

M/A-COM Technology Solutions Inc. All rights reserved.

Information in this document is provided in connection with M/A-COM Technology Solutions Inc ("MACOM") products. These materials are provided by MACOM as a service to its customers and may be used for informational purposes only. Except as provided in MACOM's Terms and Conditions of Sale for such products or in any separate agreement related to this document, MACOM assumes no liability whatsoever. MACOM assumes no responsibility for errors or omissions in these materials. MACOM may make changes to specifications and product descriptions at any time, without notice. MACOM makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MACOM FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MACOM SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.